1.1 JESD204B/C: fundamentos y arquitectura de alto nivel

1.2 Componentes del enlace: ADC/DAC front-ends, capa de enlace y PHY

1.3 Parámetros de diseño clave: número de carriles (L), número de dispositivos (M), modo Subclass y velocidad por carril

1.4 Modos de sincronización y determinismo: SYSREF, Subclass 0/1 y presupuesto de jitter

1.5 Estructura de frames y mapeo de datos: frames, multiframe y asignación a carriles

1.6 Topologías de enlace e interoperabilidad: punto a punto, multi-lane y integración con front-ends analógicos

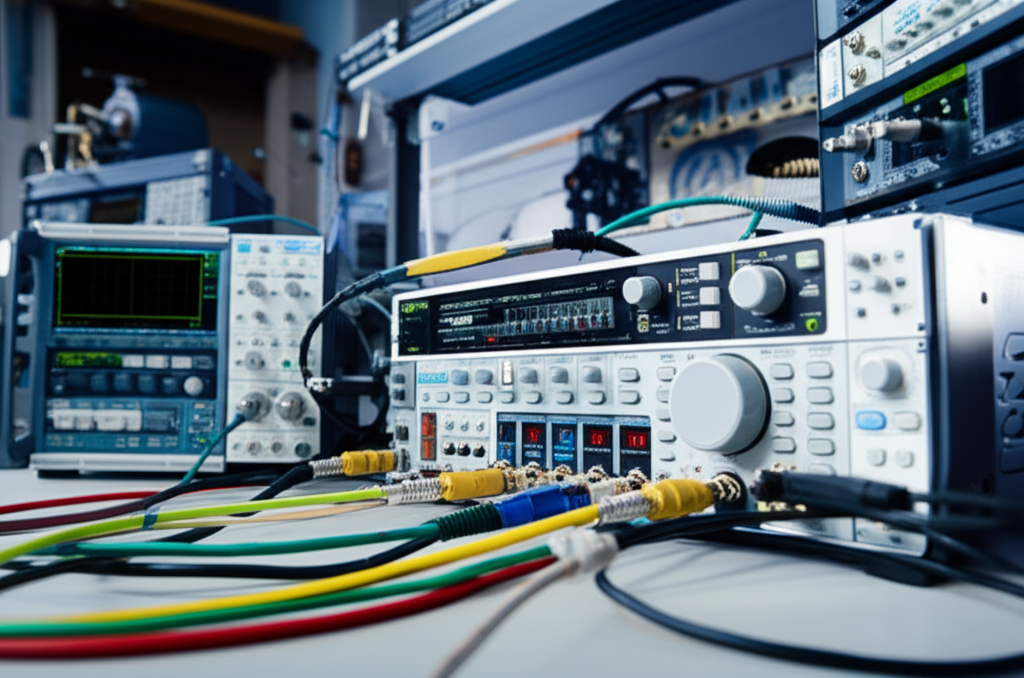

1.7 Pruebas y conformidad: patrones de prueba, verificación de rendimiento y criterios de aceptación

1.8 Diseño e integración de front-ends analógicos: ancho de banda, ganancia, impedancia y anti-aliasing

1.9 Implementación en hardware: IP JESD204, transceptores SERDES, clocking y integración con FPGA/SoC

1.10 Caso práctico: go/no-go con matriz de riesgos para validar un enlace JESD204B/C con front-ends analógicos