4.1 Arquitecturas de ADC: SAR, Delta-Sigma, Pipeline, Flash

4.2 Arquitecturas de DAC: R-2R, Ladder, Delta-Sigma, Current-Output

4.3 Diseño de PLL: tipos (integer/fractional), Detector de fase, Filtro de lazo, VCO, jitter y estabilidad

4.4 Referencias de voltaje: bandgap, ruido, deriva, estabilidad y filtración

4.5 Técnicas de reducción de ruido en diseño analógico: layout, blindaje, filtrado, separación de planos y decoupling

4.6 Interacciones entre ADC/DAC y PLL: sincronización, transferencia de jitter y límites de rendimiento

4.7 Diseño de referencia y mitigación de ruido en sistemas mixtos: buffers, aislamiento y control de tierra

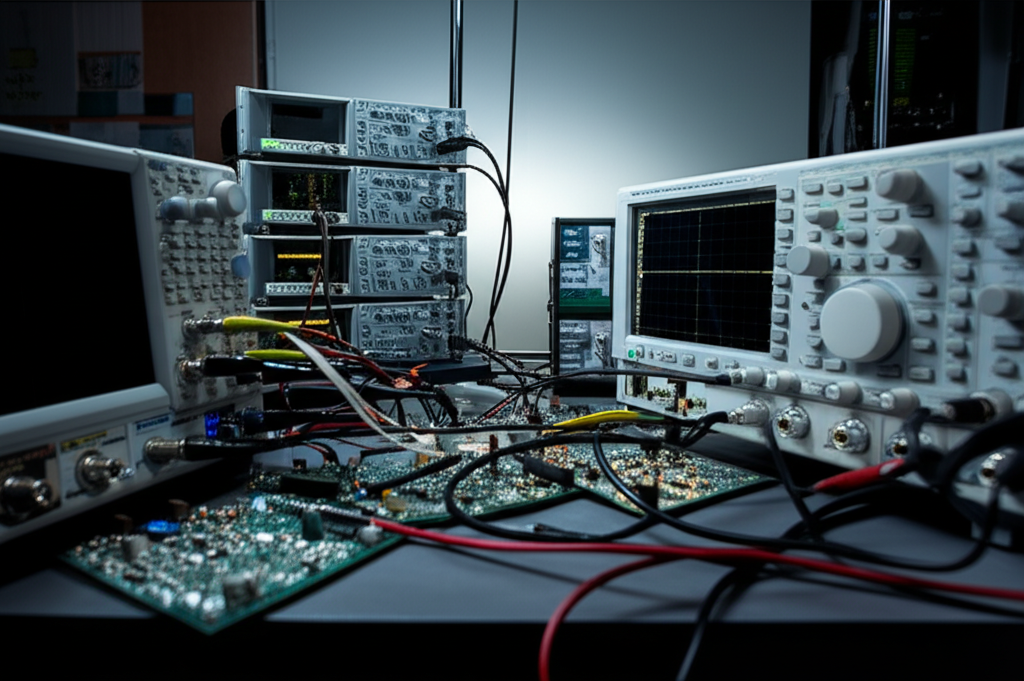

4.8 Métodos de simulación y verificación: SPICE, Cadence Spectre, ADS, MATLAB, análisis de ruido y tolerancias

4.9 Ensayos y verificación de rendimiento: SNDR/SNR, INL/DNL, linealidad, temperatura y proceso

4.10 Caso práctico: diseño integrado de un ADC/DAC con PLL y referencia de baja deriva para un sistema naval